In questa pagina sono mostrate alcune caratteristiche delle memorie allo stato solido, cioè realizzate con dispositivi semiconduttori.

Il riferimento è alle memorie attualmente utilizzate nei computer ordinari e nei microcontrollori.

Una memoria si indica come volatile se il suo contenuto è mantenuto solo in presenza di alimentazione, non volatile nel caso contrario.

In realtà tale confine non è così netto come potrebbe sembrare dalla definizione:

Prima di illustrare la struttura delle memorie e le varie tipologie è utile fare alcune precisazioni su come viene misurata la quantità di informazioni in esse contenute. Due i motivi:

L'unità di misura fondamentale è il bit che non ha un simbolo a differenza di altre unità di misura e va sempre scritto per esteso; a volte si usa la lettera b minuscola, ma si tratta di una scelta arbitraria anche se tollerata.

Un byte è formato da otto bit; il suo simbolo è la lettera B maiuscola, scelta in controtendenza rispetto alla prassi di dedicare le maiuscole alle sole unità di misura che derivano dal nome di persone (s per secondo, W per watt, da James Watt).

Una word è un insieme non meglio definito di bit, in genere variabile da 16 a 64 bit a seconda dell'unità di elaborazione in cui viene utilizzata.

Per i prefissi moltiplicativi è possibile usare le stesse lettere delle usuali unità di misura: k per 103, M per 106, G per 109. Questa è la scelta normalmente fatta nei sistemi di telecomunicazione: per esempio 1 Gbit/s significa 1 000 000 000 bit/s.

In alternativa è possibile usare sia per i bit che per i byte i prefissi Ki per 210 (per esempio 1 024 bit equivalgono a 1 kibit), Mi per 220 (1 048 576), Gi per 230 (1 073 741 824), Ti per 240 (1 099 511 627 776). Questa è la scelta normalmente fatta nei sistemi informatici: per esempio un SSD da 1 TiB contiene 1 099 511 627 776 B, circa 1,1 TB).

Nasce un'ambiguità: ad uno sguardo distratto, 1 TB è uguale ad un TiB quando invece esiste una differenza che potrebbe essere significativa. Spesso, per comodità o per pratica commerciale poco corretta, si ignora tale differenza...

Le memorie, come tutti i circuiti digitali, sono dotate di un certo numero di ingressi e di uscite, in funzione dei bit che possono essere memorizzati in esse.

Tutte le memorie sono organizzate come un insieme ordinato di parole, ciascuna costituita da un numero fisso di bit; la singola parola può tipicamente essere costituita da 1 solo bit, da quattro bit, da 8 bit (un Byte), 16 bit, 32 bit, 64 bit. Non mancano eccezioni:

In genere una memoria necessita di un numero di ingressi dati pari alla dimensione di una parola. Inoltre necessita di un numero di uscite dati, anch'esso pari al numero di bit che costituiscono una parola. In molti casi gli stessi pin svolgono, in istanti diversi, entrambe le funzioni.

Generalmente ciascun pin del Data Bus è indicato:

Ciascuna parola è individuata da un indirizzo. Normalmente il numero di parole è una potenza di due e quindi il numero di bit che costituisce l'indirizzo può essere calcolato come logaritmo in base due del numero di parole. Forse qualche esempio chiarisce meglio questa relazione; vediamoli in una tabella:

| Numero di parole | Bit di indirizzo | Come formula | |

| 1 Ki | 1 024 | 10 | 210 |

| 4 Ki | 4 096 | 12 | 212 |

| 1 Mi | 1 048 576 | 20 | 220 |

| 2 Mi | 2 097 152 | 21 | 221 |

| 1 Gi | 1 073 741 824 | 30 | 230 |

| 8 Gi | 8 589 934 592 | 33 | 233 |

Una memoria deve essere dotata di un numero di ingressi di indirizzi pari al numero di bit di indirizzo indicati nella precedente tabella. Tale numero cresce abbastanza velocemente e quindi si sono adottate tecniche per ridurne il numero.

Generalmente ciascun pin del Address Bus è indicato con le lettere A0, A1, A2... oppure con ADDR0, ADDR1, ADDR2...

L'Address Bus è sempre un ingresso.

La capacità di una memoria indica quanti bit (o quanti byte) contiene, indicando il numero di parole e la loro dimensione. La sintassi spesso usata è capacità = numero di parole X dimensione della parola, esprimendo il tutto in bit oppure in byte

Vediamo alcuni esempi:

Come si vede è prassi ignorare la differenza tra kB e kiB...

Oltre agli ingressi/uscite dati e agli ingressi di indirizzo sono presenti numerosi altri segnali piuttosto eterogenei che, normalmente, sono ingressi. Di seguito alcuni esempi, non tutti sempre presenti:

Una memoria è descritta come 2Kx8 bit. Quanti sono gli ingressi e le uscite? Disegnare un possibile schema di questo componente. Per il disegno è opportuno fare riferimento ai punti successivi di questa attività.

Una memoria è descritta come 2Mx1 bit. Quanti sono gli ingressi e le uscite? Disegnare un possibile schema di questo componente.

Una memoria è descritta come 32Gx4 bit. Quanti sono gli ingressi e le uscite? Disegnare un possibile schema di questo componente.

Descrivere la struttura delle seguenti memorie. In particolare individuare la dimensione di una parola e la quantità di parole presenti. Descrivere inoltre la funzione dei pin del control bus presenti.

Un tempo ormai lontano le memorie non volatili usavano le seguenti tecnologie:

Attualmente tutte le memorie non volativi sono di tipo:

La tecnologie di entrambe queste memorie è concettualmente simile a quella delle EPROM, ma la scrittura è possibile usando tensioni relativamente piccole e senza l'uso di apparecchi esterni alla memoria.

Questa tecnologia ha diversi limiti:

Le memorie Flash possono essere classificate come:

A le memorie Flash vengono classificate anche in base alla struttura interna:

Nelle memorie statiche (SRAM, nota 4) un singolo bit è memorizzato in un Flip Flop. In sostanza si tratta di un insieme molto esteso di registri PIPO, ciascuno dei quali memorizza una parola e può essere letto o scritto indipendentemente dagli altri attraverso il bus dati, comune a tutti.

Le SRAM possono oggi essere costruite con due obbiettivi, in contrasto tra di loro:

Una memoria statica difficilmente supera oggi la dimensione di 128 Mibit.

Il tempo di accesso è il tempo necessaria alla memoria per fornire il dato richiesto, misurato dall'istante in cui è disponibile l'indirizzo ed eventuali altri segnali di controllo all'istante in cui il dato è disponibile in uscita (nota 7).

Il tempo di scrittura è il tempo necessario alla memoria per memorizzare un dato, misurato dall'istante in cui è disponibile l'indirizzo, il dato in ingresso ed eventuali altri segnali di controllo all'istante in cui il processo termina (nota 7).

Le memorie dinamiche (DRAM) utilizzano un condensatore per memorizzare un bit.

Il vantaggio è la dimensione della singola cella enormemente minore rispetto a quella di una cella SRAM e quindi la possibilità di realizzare memorie molto più capienti a parità di costo. Oggi è per esempio normale usare singoli circuiti integrati con capacità di 16 Gbit o più, organizzati come 1Gx16 oppure 4Gbx4.

Lo svantaggio è che un condensatore tende a scaricarsi col passare del tempo e quindi le singole celle devono periodicamente essere sottoposte a refresh del contenuto, cioè alla riscrittura del contenuto, operazione gestita normalmente dal controller della memoria. Tipicamente il ciclo di refresh si misura in decine di millisecondi.

Due osservazioni in merito al numero di piedini fisici che costituiscono l'address bus:

La scelta naturale è quindi quella di fornire l'indirizzo diviso in due metà, prima l'indirizzo della riga (segnalato da un apposito piedino di Row Address Select, RAS), quindi quello della colonna (Column Address Select, CAS). Questa tecnica permette inoltre di ottimizzare i tempi di accesso quando le celle da leggere o scrivere appartengono alla stessa riga: in questo caso basta fornire solo l'indirizzo della colonna e quindi la lettura del dato è più veloce rispetto alla lettura di una cella appartenente ad un'altra riga.

Il tempo di accesso ed il tempo di scrittura sono definiti in modo analogo a quanto riportato per le memorie statiche, tenendo conto che in genere cambia se due dati successivi vengono letti o scritti nella stessa riga o in due righe diverse.

Le attuali DRAM sono in genere sincronizzate da un clock (Synchronous Dynamic Random Access Memory, SDRAM, nota 4). In linea di massima più alto è il clock, più veloce è la lettura o la scrittura della memoria. Per esempio una memoria con clock (massimo) pari 3200 MHz ha una velocità doppia di una memoria con clock (massimo) a 1600 MHz.

In realtà le operazioni di lettura e scrittura sono piuttosto articolate e richiedono numerosi cicli di clock per essere completate; questo fatto viene spesso espresso da alcuni numeri (latenza) che rappresentano il numero di cicli di clock necessari per completare vari tipi di operazioni (per esempio lettura di una cella qualunque oppure lettura di più celle consecutive oppure scritture...).

Rimane un dubbio: meglio una memoria con clock elevato oppure con latenza inferiore? Non esiste una risposta univoca...

Il tempo di accesso ed il tempo di scrittura sono definiti in modo analogo a quanto riportato per le memorie statiche, tenendo conto che in genere cambia se due dati successivi vengono letti o scritti nella stessa riga o in due righe diverse. Spesso tali tempi sono misurati in intervalli di clock anziché in secondi.

A differenza dei Flip Flop che sono attivati dal fronte di salita oppure da quello di discesa del clock, le SDRAM moderne sono attivate da entrambi i fronti, dando origine a memorie che, a parità di clock, sono due volte più veloci (DDR SDRAM, Double Data Rate SDRAM).

Esistono varie famiglie, tra di loro incompatibili di DDR; DDR(1), DDR2, DDR3, DDR4 (la versione attualmente più diffusa). DDR5... Normalmente tra una generazione di DDR e l'altra si assiste ad un aumento della frequenza di clock, ad un aumento della latenza (aspetto negativo ampiamente compensato dall'aumento della frequenza di clock), ad una diminuzione del consumo di energia e ad aumento della capacità massima.

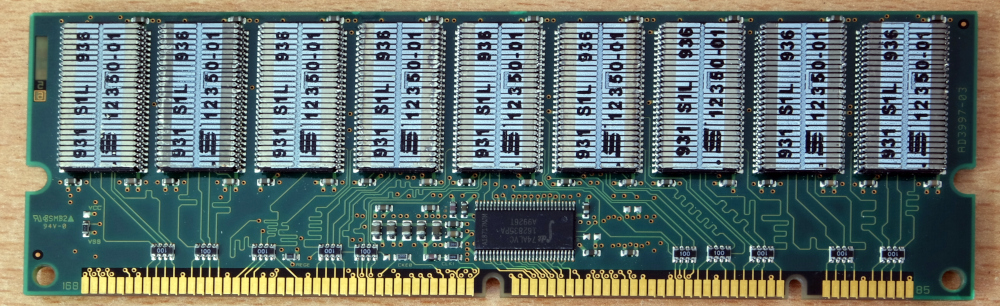

Spesso un singolo circuito integrato non è sufficiente per garantire la necessaria capacità di memoria necessaria ad una determinata applicazione. La soluzione è riunire più integrati al fine di aumentare il numero e/o la dimensione delle parole, costruendo un banco di memoria.

L'esempio più familiare è costituito dalla memoria dei PC. Di seguito qualche esempio... storico.

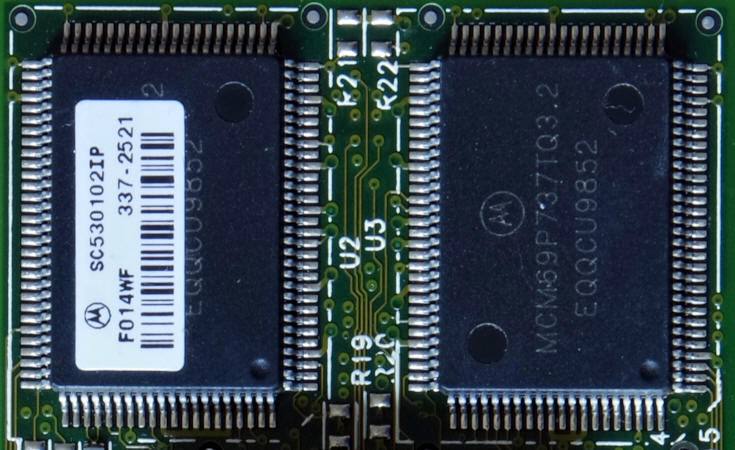

L'immagine seguente mostra due chip MCM69P737, memoria sincrona statica spesso usata come cache L2 ad inizio secolo; ciascun chip ha organizzazione 128Kx36 bit, per una capacità complessiva di 128Kx72 bit.

Spesso i moduli DIMM moderni possiedono più pin di alimentazioni, a volte con tensioni diverse:

Simulare con Deeds il funzionamento delle memorie contenute nel file memoria.zip, come di seguito descritto.

Il file 0-RAM.pbs contiene una memoria RAM 256x4 bit, con ingresso ed uscita dei dati su bus separati. Non serve disegnare il circuito in quanto contenuto nel file compresso memoria.zip.

Per osservare il contenuto della memoria occorre cliccare sulla memoria stessa; il contenuto può essere visto sia in binario che in esadecimale. All'inizio della simulazione il contenuto della memoria non è definito (contiene "?").

Come procedere:

Il file 1-SRAM.pbs contiene una memoria sincrona. In aggiunta a quanto già visto nella precedente attività occorre attivare anche il clock, attivo sul fronte di salita. Per l'uso del bus in Deeds si rimanda alla pagina relativa al simulatore Deeds.

Procedere come indicato nell'attività 2.0.

Il file 2-SRAM-HZ.pbs contiene una memoria 4Kx8 bit con un unico bus dati per l'ingresso e l'uscita dei dati. Utile rivedere la logica 3-state.

Procedere come indicato nell'attività 2.0.

Il file 3-RAM_Bank_256x4.pbs contiene un banco costituito di quattro memorie 256x4 bit che ha lo scopo di aumentare la dimensione di una parola da 4 a 16 bit.

Procedere come indicato nell'attività 2.0. In particolare evidenziare dove vengono scritti i 16 bit che costituiscono una singola parola.

Il file 4-SRAM_bank_4kx8.pbs contiene un banco di quattro memorie 1Kx8 bit che ha lo scopo di aumentare il numero di parole, ottenendo un banco 4Kx8. Utile rivedere i decoder.

Procedere come indicato nell'attività 2.0. In particolare evidenziare dove vengono scritti i dati nel caso in cui la parte più significativa dell'indirizzo vale 00 oppure 01 oppure 10 oppure 11.

Analizzare il modulo di memoria per PC KF432C16BBK2_32. Individuare la tecnologia, la capacità, la frequenza di clock e la latenza, le tensioni di alimentazione.

Analizzare il modulo di memoria per PC KF556C40BB-32. Individuare la tecnologia, la capacità, la frequenza di clock e la latenza, le tensioni di alimentazione.

[ Avanzato ] Analizzare la struttura della memoria del proprio PC, tramite osservazione diretta, ricerca di documentazione oppure software dedicato.

Queste memorie hanno lo scopo di ridurre al minimo il numero piedini di ingresso ed uscita, permettendo di realizzare memorie con capacità relativamente elevata in contenitori con pochi pin, tipicamente otto, inclusa l'alimentazione.

L'organizzazione è quella tipica delle memorie appena descritte, ma i bit dati vengono letti o scritti serialmente, attraverso un solo pin di ingresso ed un solo pin di uscita (oppure un solo pin di input/output). Analogamente i bit di indirizzo sono impostanti sfruttando un solo pin di ingresso, in genere coincidente con l'ingresso dati.

Per esempio 48L512 è una memoria RAM statica 64Kx8 bit. Dati ed indirizzi vengono scritti utilizzando l'ingresso condiviso SI (Serial Input) e letti dall'uscita SO (Serial Output). Di seguito il pin-out, 8 pin in totale, inclusa l'alimentazione:

Nelle fotografie sopra riportate è visibile sia sulla DIMM che sulla SO-DIMM una memoria di questo tipo, di tipo EEPROM: ha il compito di memorizzare i parametri di funzionamento della memoria DRAM (tipo, quantità, velocità...) e permettere così al PC di configurarsi autonomamente all'avvio. Quando ha questa funzione viene indicata some Serial Presence Detect EEPROM (SPD), in genere con interfaccia Inter Integrated Circuit.

Le memorie FIFO (First In, First Out) sono memorie volatili ad accesso non casuale: i dati sono scritti attraverso i pin di ingresso e letti attraverso i pin di uscita senza specificare alcun indirizzo: semplicemente la prima parola scritta sarà la prima ad essere letta e, una volta letta, viene "distrutta".

Di seguito i pin di un registro IDT 7208 con organizzazione interna 32Kx9 bit. Si possono vedere i nove pin di ingresso dati (D0...D8), le nove uscite (Q0... Q9) ed i pin di scrittura W e di lettura R. Quando il pin W è attivo la parola in ingresso viene scritta nell'ultima cella libera, quando R è attivo viene letta la prima cella occupata.

L'uso tipico di queste memorie è la funzione di buffer tra un generatore di dati occasionalmente molto veloce ed un ricevitore non sempre in grado di ricevere dati troppo velocemente.

Immagine tratta da Magnetic-core memory close-up, Bubba73 (Jud McCranie), CC-BY-SA-4.0

Data di creazione di questa pagina: aprile 2021

Ultima modifica: 14 marzo 2025

Appunti scolastici - Versione 0.1033 - Marzo 2026

Copyright 2012-2026, Vincenzo Villa (https://www.vincenzov.net)

Creative Commons | Attribution-ShareAlike 4.0 International (CC BY-SA 4.0)