Questa pagina descrive l'uso del modulo MSSP per la trasmissione seriale sincrone di un byte dal PIC18 ad un registro SIPO 74HC164 al quale sono collegati otto LED. A differenza di quanto richiesto nella pagina Usare un registro SIPO la trasmissione è qui realizzata con l'hardware dedicato MSSP, Master Synchronous Serial Port (nota 1)

Prima di proseguire nella lettura di questa pagina è vivamente consigliata la lettura dei fogli tecnici, avendo per esempio ben chiaro il significato del diagramma temporale riportato più avanti.

Lo schema di riferimento è piuttosto semplice:

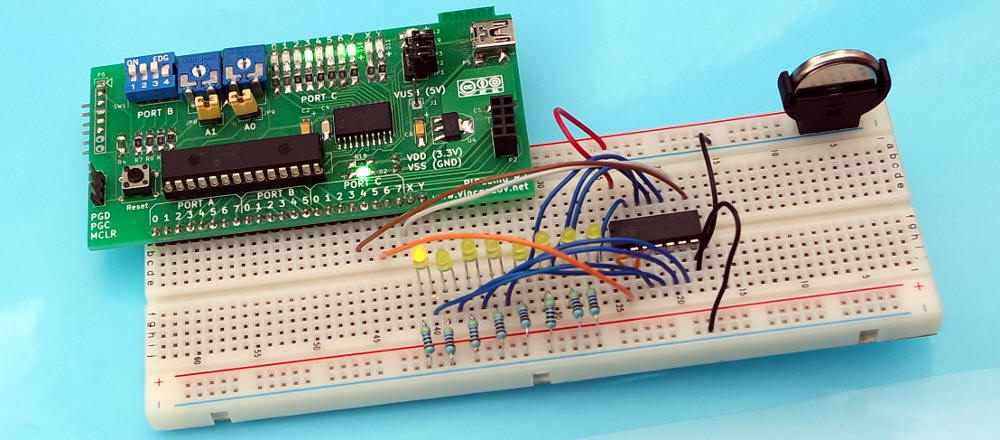

La foto di apertura mostra il circuito realizzato su breadboard utilizzando il circuito PICdemo R2

MSSP è il cuore hardware di tutte le interfacce seriali sincrone del PIC18.

Volendo semplificare al massimo, possiamo descrivere questo modulo come un registro a scorrimento in cui il processore scrive in parallelo il byte da trasmettere e l'hardware provvede alla trasmissione seriale, un bit alla volta. Lo schema a blocchi semplificato:

I due elementi principali sono:

Dei tre pin esterni gestiti dal modulo MSSP utilizzeremo solo SDO (dato seriale, in uscita dal PIC) e SCK (clock).

Il codice completo è disponibile a fondo pagina; è suddiviso in due parti, la configurazione del modulo MSSP ed il loop infinito che trasmette una sequenza di byte.

Il modulo MSSP è piuttosto complesso in quanto svolge numerose funzioni (nota 2). Di conseguenza la sua configurazione non è banale. Il nostro obbiettivo è utilizzarlo per generare un segnale seriale sincrono in grado di trasferire 8 bit, uno alla volta, sul fronte di salita del clock. La modalità che più si avvicina a ciò è la SPI Master.

Il registro principale per la configurazione del modulo MSSP è il REGISTER 17-2: SSPCON1: MSSP CONTROL 1 REGISTER (SPI MODE).

La trasmissione di un byte è semplice: basta scriverlo nell'apposito registro SSPBUF...

movff DatoTx, SSPBUF

Il reset prima della trasmissione è facoltativo in quanto l'eventuale vecchio contenuto verrebbe comunque spinto fuori dal nuovo byte. Dovesse servire, anche per chiarezza nelle prove:

bcf LATC, RC7

bsf LATC, RC7

Un'avvertenza: prima di trasmettere un secondo byte è necessario attendere che il registro SSPBUF si sia svuotato. In questa prima versione è sufficiente attendere qualche ciclo macchina (la serie dei nop nel codice)

Di seguito il diagramma temporale corrispondente. Dall'alto

Un problema della prima versione codice deriva dal fatto che non viene effettuata nessuna verifica della avvenuta trasmissione di un byte prima di trasmetterne un secondo. Nel caso dovesse succedere, il modulo rimane temporaneamente bloccato (nota 3).

Il secondo esempio utilizza il flag BF del registro SSPSTAT che vale 1 solo quando l'intero byte è stato trasmesso.(nota 4):

attendi

btfss SSPSTAT, BF

bra attendi

Questo flag non può essere azzerato direttamente, ma per predisporre il modulo MSSP alla ricezione/trasmissione di un nuovo byte è necessario leggere il registro SSPBUF: (nota 5)

movff SSPBUF, DatoRx

Ultima modifica di questa pagina: 23 maggio 2016 - Una pagina simile: PIC18 come master SPI, in C

Assembly PIC18 - Versione 0.5 - aprile 2018

Copyright 2016-2018, Vincenzo Villa (https://www.vincenzov.net)

Assembly PIC18 di Vincenzo Villa è distribuito con Licenza Creative Commons Attribuzione 4.0 Internazionale