Tutorial →

Appunti scolastici → Appunti sparsi →

La memoria

Pagina in fase di preparazione

Pagina in fase di preparazione

Struttura di una generica memoria ad accesso casuale

Una memoria ad accesso casuale (nota 1) è costituita da un certo numero di celle

identiche come dimensione, identificate da un numero progressivo (indirizzo,

ADDR). Ciascuna cella (word) contiene un numero fisso di bit

il cui significato è genericamente indicato come valore o DATA.

Per esempio le tre immagini seguenti rappresentano una memoria formata da

512 celle (quindi con indirizzo compreso tra 0 e 511) ciascuna in grado di

contenere parole con valore compreso tra 0 e 15. Le tre immagini sono

relative alla stessa identica realtà e si differenziano tra di loro solo per

la base utilizzata per rappresentare i numeri (nell'ordine: decimale,

binario, esadecimale):

- La rappresentazione nella prima tabella descrive male la realtà dei

computer e quindi non è in genere usata

- La seconda rappresenta bene la realtà delle macchine, ma è di

difficile lettura e memorizzazione per gli umani

- La terza è la "via di mezzo" più utilizzata

Per esempio, per descrivere la decima cella, evidenziata in rosso, si può

scrivere indifferentemente:

- La cella con indirizzo 9 contiene il valore

1

- La cella con indirizzo 0b1001 contiene il valore

0b1 (è stata utilizzata la sintassi presa a

prestito da alcuni compilatori C per rappresentare i numeri binari,

premettendo 0b). Quando i numeri diventano grandi questa

rappresentazione diventa inutilizzabile per gli umani.

- La cella con indirizzo 0x9 contiene il valore

0x1 (è stata utilizzata la sintassi presa a prestito

dal C per rappresentare i numeri esadecimali, premettendo 0x)

Spesso è necessario rappresentare il contenuto di molte celle. In questo

caso l'uso di una tabella che riporta per ciascuna cella indirizzo e

contenuto occupa molto spazio... Per questo si preferisce a volte riportare

il contenuto di più celle su una sola riga, riportando solo per la prima

cella l'indirizzo.

Per esempio la seguente tabella (nota 2) mostra il

contenuto di 176 celle di memoria (11 righe, ciascuna con il valore di 16

celle consecutive):

- La prima colonna riporta in esadecimale gli indirizzi, da 0x00000000

a 0x000000A0, saltando di 16 in 16

- La prima riga riporta il contenuto delle 16 celle con indirizzo

0x00, 0x01 ... 0x0F

- L'ultima riga riporta il contenuto delle 16 celle con indirizzo

0xA0, 0xA1.... 0xAF

Per esempio:

- La cella con indirizzo 0x00000000 contiene il calore 0x25 (in verde)

- La cella con indirizzo 0x00000012 contiene il valore 0x0A (in rosso)

- Quale è il contenuto della della con indirizzo 0x000000AB? (nota

3)

Di seguito due esempi tratti da due diversi programmi reali utilizzati

per scrivere codice:

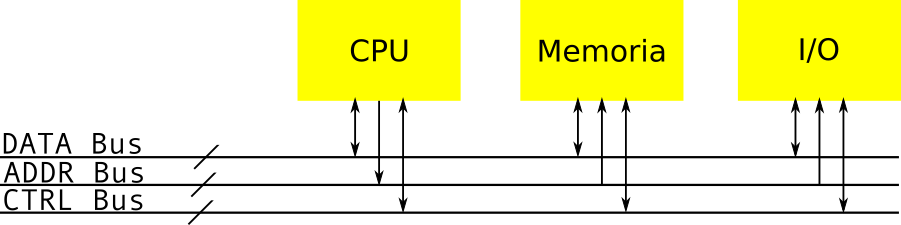

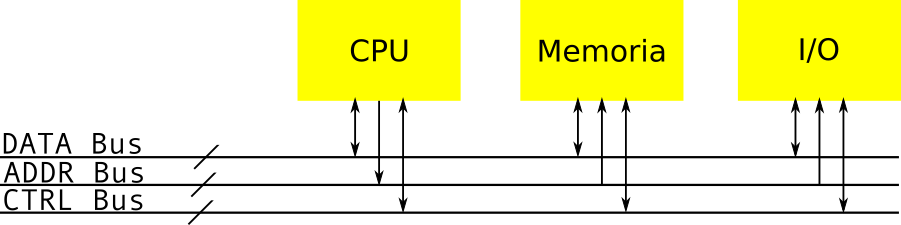

Architettura di Von Neumann

La macchina di Von Neumann (o stored-program computer) è caratterizzata

dall'avere:

- Una CPU

- Una memoria contenente dati e istruzioni (programmi)

- Una serie di dispositivi di ingresso/uscita (che in seguito

ignoreremo)

I collegamenti tra i tre blocchi sono realizzati tramite bus (nota

4), ciascuno capace di trasportare un numero anche elevato di bit:

- Un DATA Bus che trasporta i dati tra CPU e memoria oppure viceversa

(si noti la doppia freccia che indica questo bus come bidirezionale).

Questo bus deve essere in grado di trasportare tanti bit quanto è la

dimensione di una parola.

- Un ADDR Bus che indirizza la cella di memoria da cui il dato deve

essere letto o in cui deve essere scritto (si noti la freccia che indica

questo bus come unidirezionale). Questo bus deve essere in grado di

trasportare tanti bit quanti sono necessari per indirizzare ciascuna

cella di memoria.

- Un CTRL Bus che trasporta i segnali di controllo: per esempio il

comando di lettura o di scrittura

Per esempio, in riferimento alla seguente figura:

- Il DATA Bus è formato da 8 bit (in pratica: 8 fili)

- L'ADDR Bus è formato da 32 bit (in pratica 32 fili)

Quesito: da quanti bit sono formati DATA e ADDR Bus per gli altri due

esempi mostrati in questa pagina?

La macchina di Von Neumann viene spesso considerata l'architettura su cui

si basano i computer attuali, perlomeno quelli di uso generico, perché

permette la massima flessibilità nel scegliere quanta memoria assegnare alle

istruzioni e quanta ai dati.

Il fatto che la memoria sia unica porta però ad alcuni compromessi:

- La presenza di un solo Bus per indirizzi e dati costituisce un

collo di bottiglia che rallenta il funzionamento del computer.

- Istruzioni e dati devono avere la stessa dimensione

- L'intera memoria deve essere a lettura/scrittura (e quindi in genere

volatile)

Per un

approfondimento.

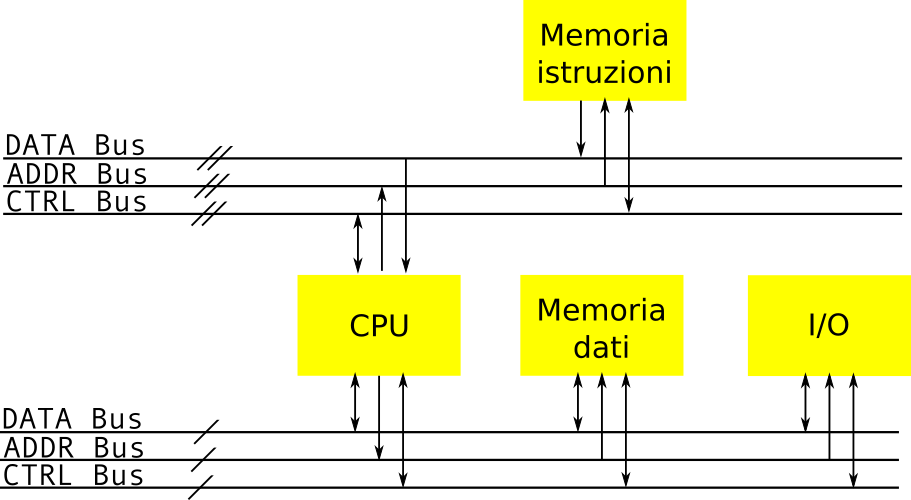

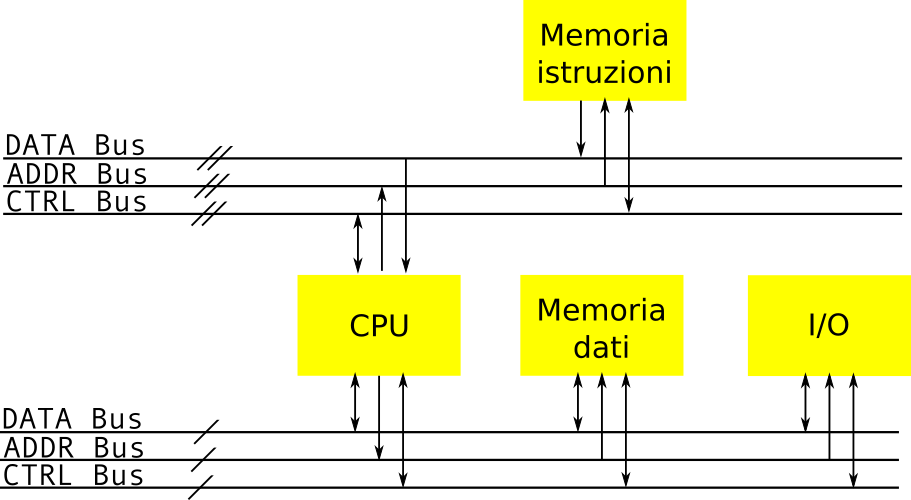

Architettura Harvard

Una architettura di tipo Harvard possiede:

- Una CPU

- Una memoria contenente istruzioni (programmi)

- Una memoria contenente dati

- Una serie di dispositivi di ingresso/uscita (che in seguito

ignoreremo)

Una macchina di tipo Harvard è poco flessibile e quindi è adatta solo per

sistemi che eseguono programmi che non cambiano nel tempo,

Ha diversi vantaggi:

- Permette maggiori prestazioni in quanto istruzioni e dati possono

essere letti contemporaneamente. Praticamente questo porta ad un

raddoppio della velocità

- Le due memorie possono avere lunghezza di parola diversa

- La memoria programma può essere di tipo non volatile, evitando

quindi la fase di boot (ottenendo quindi una partenza "istantanea" dopo aver fornito

alimentazione). Si noti il verso dei dati unidirezionale dalla memoria

programma alla CPU, tipico di questa architettura

Per un

approfondimento.

Quanto detto è oggi in parte superato e la realtà è più articolata:

- Molti sistemi indicati come Harvard in realtà sono modified

Harvard architecture al fine di rendere meno rigida la separazione tra

le due memorie.

- Quasi tutte le CPU moderne usate in computer con architettura di Von Neumann

hanno internamente una architettura Harward con due memorie cache, una

per i dati ed una per le istruzioni, al fine di migliorare sensibilmente

le prestazioni.

Note

- Quanto descritto in questa pagina fa riferimento indifferentemente

sia alle memorie volatili (in genere indicate con il termine RAM, Randon

Access Memory) che alle memorie non volatili (in genere oggi

identificate con le memorie Flash).

- L'immagine è stata ottenuta con il comando Linux

hexdump

- Il valore della cella con indirizzo 0x000000AB è 0x93

- Questa architettura andrebbe più propriamente indicata come

System Bus

Data di creazione di questa pagina: settembre 2017

Ultima modifica: 4 ottobre 2017